# Atari ST System-on-Chip in VHDL

Individual Project UFEEJ4-40-3

Author: Lyndon Amsdon Student Number: 05500164

> Word Count 15116

# **Table of Contents**

| Paragraph Number | Title                    | Page Number |

|------------------|--------------------------|-------------|

|                  | Chapter 1 - Introduction |             |

| 1.1              | Preface                  | 1-1         |

| 1.2              | Introduction             | 1-1         |

| 1.2.1            | TV Boy                   | 1-1         |

| 1.2.2            | Flashback 2              | 1-2         |

| 1.2.3            | NOAC                     | 1-2         |

| 1.2.4            | MSX Bazix                | 1-3         |

| 1.2.5            | Minimig                  | 1-3         |

| 1.2.6            | C-One/C64DTV             | 1-4         |

# Chapter 2 - In Depth Introduction

| 2.1              | Atari History                                                                                                                                                                                                                                              | 2-1         |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| 2.1.1            | Atari ST Models                                                                                                                                                                                                                                            | 2-1         |  |

| 2.2              | Atari ST Models2-1Atari ST Hardware2-2MC68000 CPU2-4GLUE custom semiconductor2-4MMU custom semiconductor2-5SHIFTER custom semiconductor2-5DMA custom semiconductor2-5MFP MC689012-6Yamaha YM21492-6ACIA MC68502-6FDC WD17722-6Atari ST Operating System2-8 |             |  |

| 2.2.1            | MC68000 CPU                                                                                                                                                                                                                                                | 2-4         |  |

| 2.2.2            | GLUE custom semiconductor                                                                                                                                                                                                                                  | 2-4         |  |

| 2.2.3            | MMU custom semiconductor                                                                                                                                                                                                                                   | 2-5         |  |

| 2.2.4            | SHIFTER custom semiconductor                                                                                                                                                                                                                               | 2-5         |  |

| 2.2.5            | DMA custom semiconductor                                                                                                                                                                                                                                   | 2-5         |  |

| 2.2.6            | MFP MC68901                                                                                                                                                                                                                                                | 2-6         |  |

| 2.2.7            | Yamaha YM2149                                                                                                                                                                                                                                              | 2-6         |  |

| 2.2.8            | ACIA MC6850                                                                                                                                                                                                                                                | 2-6         |  |

| 2.2.9            | FDC WD1772                                                                                                                                                                                                                                                 | 2-6         |  |

| 2.3              | Atari ST Operating System                                                                                                                                                                                                                                  | 2-8         |  |

| Paragraph Number | Title                                                                                                                                                                                                                                                      | Page Number |  |

2.3.1Atari ST Boot Up Operation2-8

Chapter 3 – Research

| FPGA                      | 3-1                                                                                                                                                        |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Base Hardware             | 3-2                                                                                                                                                        |

| IP Cores                  | 3-3                                                                                                                                                        |

| Software Suite            | 3-3                                                                                                                                                        |

| Processor                 | 3-3                                                                                                                                                        |

| Books and literature      | 3-4                                                                                                                                                        |

| Debugging                 | 3-5                                                                                                                                                        |

| Operating System Versions | 3-6                                                                                                                                                        |

| System Memory             | 3-7                                                                                                                                                        |

| Serial Port               | 3-8                                                                                                                                                        |

| Video Output              | 3-9                                                                                                                                                        |

|                           | Base Hardware<br>IP Cores<br>Software Suite<br>Processor<br>Books and literature<br>Debugging<br>Operating System Versions<br>System Memory<br>Serial Port |

Chapter 4 – Design

| Paragraph Number | Title               | Page Number |

|------------------|---------------------|-------------|

| 4.1.10           | Keyboard and Mouse  | 4-8         |

| 4.1.9            | RS232 Serial        | 4-7         |

| 4.1.8            | Floppy Disk Drive   | 4-6         |

| 4.1.7            | VGA                 | 4-5         |

| 4.1.6            | 5v PCI I/O          | 4-5         |

| 4.1.5            | OS and Flash Memory | 4-4         |

| 4.1.4            | Debugging           | 4-3         |

| 4.1.3            | Static RAM          | 4-3         |

| 4.1.2            | MC68SEC000 CPU      | 4-2         |

| 4.1.1            | Base Hardware       | 4-1         |

| 4.1              | Components          | 4-1         |

| 4.2  | Design Differences            | 4-8  |

|------|-------------------------------|------|

| 4.3  | Process of Implementation     | 4-11 |

|      |                               |      |

|      | Chapter 5 – Implementation    |      |

|      |                               |      |

| 5.1  | Flashing LED                  | 5-1  |

| 5.2  | VGA Colour pattern            | 5-1  |

| 5.3  | Writing bytes to Flash Memory | 5-2  |

| 5.4  | Writing file to Flash Memory  | 5-5  |

| 5.5  | CPU                           | 5-5  |

| 5.6  | Reset                         | 5-6  |

| 5.7  | Clock                         | 5-6  |

| 5.8  | Synchronous Bus interface     | 5-7  |

| 5.9  | Flash data bus resizing       | 5-8  |

| 5.10 | 7 Segment Display             | 5-9  |

| 5.11 | Single Step                   | 5-10 |

| 5.12 | Glue IP core                  | 5-10 |

| 5.13 | MMU IP core                   | 5-13 |

| 5.14 | Hardware Breakpoint           | 5-16 |

| 5.15 | Shifter IP Core               | 5-17 |

| 5.16 | MFP IP Core                   | 5-17 |

| 5.17 | ACIA IP Core                  | 5-19 |

| 5.18 | YM2149 IP Core                | 5-20 |

| 5.19 | DMA IP Core                   | 5-21 |

| 5.20 | FDC IP Core                   | 5-22 |

| 5.21 | Eiffel PS/2 Conversion        | 5-24 |

| 5.22 | IDE Compact Flash             | 5-26 |

|      |                               |      |

| Paragraph Number | Title                                | Page Number |  |

|------------------|--------------------------------------|-------------|--|

|                  | Chapter 6 – Testing and verification |             |  |

| 6.1              | Benchmarking                         | 6-z         |  |

| 6.2              | Colour Palette                       | 6-z         |  |

| 6.3              | Sound Techniques                     | 6-z         |  |

| 6.4              | Software Over Scan                   | 6-z         |  |

|                  | Chapter 7 – Future ideas             |             |  |

| 7.1              | Floppy Drive Emulation               | 7-1         |  |

| 7.2              | MIDI                                 | 7-1         |  |

| 7.3              | IDE                                  | 7-2         |  |

| 7.4              | Unification of mass storage          | 7-2         |  |

| 7.5              | Reconfigurable systems               | 7-3         |  |

| 7.6              | Commercial viability                 | 7-3         |  |

|                  | Chapter 8 – Summary                  |             |  |

| 8.1              | Summary                              | 8-1         |  |

# List of Illustrations

| Figure Number | Title                         | Page Number |

|---------------|-------------------------------|-------------|

| 1             |                               | 1 1         |

| 1             | TV Boy                        | 1-1         |

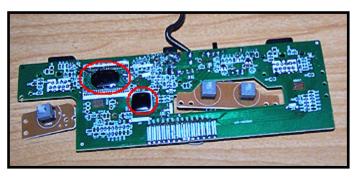

| 2             | Flashback 2 PCB               | 1-2         |

| 3             | NOAC SOC                      | 1-2         |

| 4             | MSX Bazix Unit                | 1-3         |

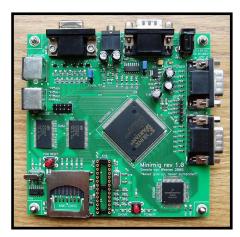

| 5             | Minimig PCB                   | 1-3         |

| 6             | C64DTV                        | 1-4         |

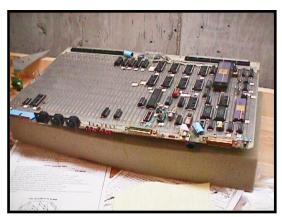

| 7             | Atari ST CPU Prototype        | 2-2         |

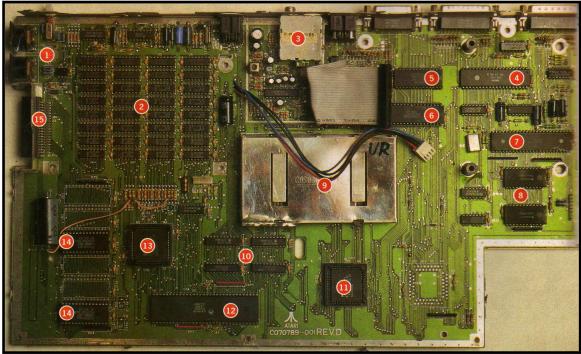

| 8             | Atari STfm Motherboard        | 2-3         |

| 9             | Atari ST boot up sequence     | 2-7         |

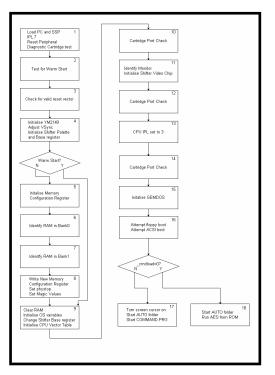

| 10            | Xilinx FPGA block layout      | 3-1         |

| 11            | Flash memory organisation     | 3-6         |

| 12            | DAC using resistor ladders    | 3-9         |

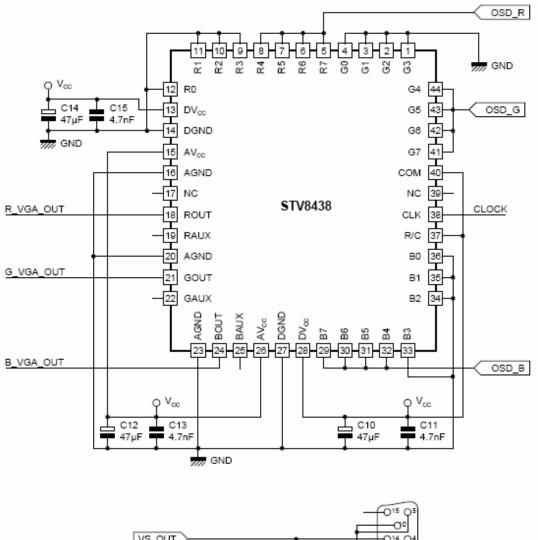

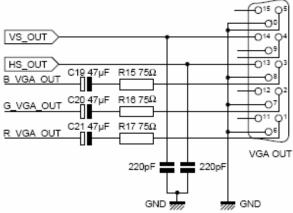

| 13            | Specialised video DAC         | 3-10        |

| 14            | Enterpoint Raggedstone        | 4-1         |

| 15            | VGA video timing              | 4-5         |

| 16            | RS232 to TTL level translator | 4-7         |

| 17            | ATX pin description           | 4-9         |

| 18            | Design Block diagram          | 4-10        |

| 19            | Architecture for LED Flash    | 5-1         |

| 20            | Colour test display           | 5-2         |

| 21            | Flash Programmer menu         | 5-2         |

| 22            | MCS file format               | 5-5         |

| 23            | Synchronous bus interface     | 5-8         |

| 24            | Flash state machine           | 5-8         |

| 25            | 7 segment display             | 5-9         |

| 26            | Address decoding in Glue      | 5-11        |

| 27            | MC68000 start up sequence     | 5-11        |

Figure Number

Title

Page Number

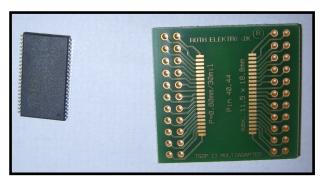

| 28 | SRAM and adapter PCB           | 5-13 |

|----|--------------------------------|------|

| 29 | Refresh Address removal        | 5-13 |

| 30 | Refresh RAS removal            | 5-14 |

| 31 | SRAM signal creation           | 5-14 |

| 32 | Single Step DTACK creation     | 5-16 |

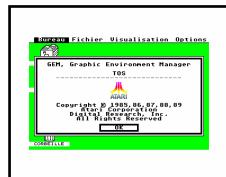

| 33 | Photo of Desktop               | 5-18 |

| 34 | Xilinx ISE DLL error           | 5-18 |

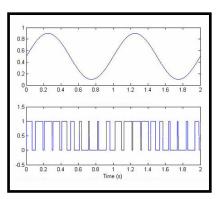

| 35 | PWM Sound                      | 5-20 |

| 36 | Excerpt from OS                | 5-22 |

| 37 | FDCSn from wf25913ip_ctrl.vhd  | 5-22 |

| 38 | T1_VERIFY_CRC state            | 5-23 |

| 39 | WD1772 delay state             | 5-24 |

| 40 | Playstaion controller protocol | 5-25 |

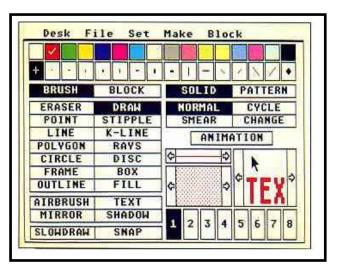

| 41 | Degas Elite                    | 6-1  |

| 42 | Change to Shifter              | 6-2  |

| 43 | SND Player                     | 6-3  |

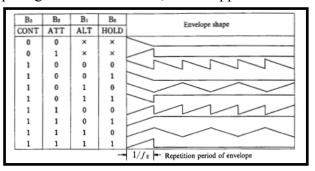

| 44 | Envelope Shapes                | 6-3  |

| 45 | Old enveloper generator        | 6-4  |

| 46 | New enveloper generator        | 6-4  |

| 47 | Screen borders                 | 6-4  |

|    |                                |      |

# List of Tables

| Table Number | Title                                 | Page Number |

|--------------|---------------------------------------|-------------|

|              |                                       |             |

| 1            | Atari ST models                       | 2-2         |

| 2            | Xilinx development boards             | 3-2         |

| 3            | MC68000 family processors             | 3-4         |

| 4            | TOS versions                          | 3-6         |

| 5            | Serial port pin description           | 4-7         |

| 6            | Flash memory commands                 | 5-4         |

| 7            | FPGA connections to 7 segment display | 5-9         |

| 8            | Start of Operating System             | 5-11        |

| 9            | Memory Configuration register         | 5-16        |

| 10           | IPL Encoding                          | 5-18        |

| 11           | Playstation controller packet         | 5-24        |

| 12           | Colour palette error                  | 6-2         |

|              |                                       |             |

# **Chapter 1**

# Preface

# 1.1

Within this personal project is a complete guide to the research, development, implementation and conclusions to creating a System on Chip, based on the Atari ST series of home microcomputer which spanned a production date of 1985-1993 [1]. The project is designed to be left open to continual work and extensions beyond the original Atari ST design.

This document assumes prior knowledge of Microsystems design and the Motorola MC68000 CPU, and going in depth into these topics is beyond the scope of this document.

# Introduction and Overview

# 1.2

This project is inspired by other enthusiast's attempts at creating systems on chip that faithfully reproduce early home microcomputers and arcade machines. The development in the last few years in programmable logic devices, with increased logic elements and low development costs, has meant it is possible to fit entire computers into one semiconductor.

# 1.2.1

# TV Boy

One of the first commercially available products has to be the 'TV Boy', which was an unlicensed reverse engineered copy of the Atari 2600. It first went on sale around the mid 1990s. The original Atari 2600 used 4Kbyte game cartridges whereas the TV Boy used a

Figure 1 - TV Boy

512Kbyte ROM as storage for the 127 internal games [2]. A spare 4Kbyte slot was used as the game menu selection. As it was unlicensed by Atari the games had different names and some had very small changes to the graphical details. All the digital electronics were designed into a single ASIC, intended for mass production and low cost.

### 1.2.2

### Flashback 2

There have been some official licensed Atari consoles recreated in modern silicon. The Flashback 2 is another Atari 2600 with 40 games included. The design of the case is reminiscent of the original Atari 2600, but being somewhat Figure 2 - Flashback 2 Main PCB smaller and lighter. The Flashback

2 was designed by Curt Vendel and Legacy Engineering, and in an interview Curt Vendel remarked that the "Flashback 2 did exceptionally well with 860,000 sold in the U.S./domestic" [3].

#### 1.2.3

#### NOAC

Another unlicensed reversed engineered copy of a console exists, based on Nintendo's NES (Nintendo Entertainment System). These are known as NOAC (Nintendo On A Chip) and originate from a variety of manufactures in China and are inaccurate in many ways to an original NES [4]. The Integrated Circuit is supplied without a real physical package, instead being covered with an epoxy glue material.

Figure 3 - NOAC SOC

A brief look on the internet at current and past projects in this particular field has shown the following popular home computers being implemented into FPGAs.

- Msx Bazix MSX (Japanese home computer)

- Minimig Amiga A500

- Suska Atari ST/STE

- C-One Reconfigurable Commodore 64 & Commodore VIC-20

### 1.2.4

### **MSX Bazix**

The MSX Bazix [5] was a project led to create primarily a clone of the technically advanced MSX home computer, which was very popular in Japan in the 1980s. The MSX Bazix was also designed to pave the way for other developers to create projects on, with the design of the hardware being open source and an array of I/O ports to cater for most needs. It's future and success is unknown with no news on their website for over 2 years.

Figure 4 - MSX Bazix Unit

#### 1.2.5

### Minimig

The Minimig (short for Mini Amiga) is based around a Xilinx FPGA and MC68SEC000 CPU. It has some key changes from the original Amiga 500, including support for a PS/2 mouse and keyboard and games that load from a removable MMC Flash memory device [6]. The source code for both the FPGA and PIC microcontroller became available to download on 24/07/2007 and the hardware is available to buy through online resellers.

Figure 5 - Minimig PCB

### 1.2.6

### C-One/C64DTV

Many other exist, at various stages of completion. What are more interesting are the results of some of these projects. The best example of this is the C-One. The C-one was designed by Jeri Ellsworth in 2002, to replicate a Commodore 64 using an Altera FPGA [7]. By 2004 a marketing company had approached Jeri Ellsworth to use the design in a low cost hand held console to plug directly into a TV, the result being the C64DTV.

The C64DTV hardware is all based on an ASIC, or Application Specific Integrated Circuit, which is like a fixed design FPGA. These are commonly used in mass produced products. The software comprised of 30 games, originally produced for the Commodore 64 in the mid to late eighties and licensed to be used. The C64DTV was very successful on release, selling 70,000 units in a single day via a TV shopping channel priced around £20[8].

Figure 6 - C64DTV

# **Chapter 2**

# In Depth Introduction

# 2.1

Atari was founded in 1972 by Nolan Bushnell and Ted Dabney firstly creating arcade games, and then moving onto home computers and home video game consoles. Atari at the time had created groundbreaking games like Pong, and also designed an affordable 8 bit home video game console, called the 2600 based around the Motorola 6502 CPU.

By 1976 Atari was sold to Time-Warner and work had started on a replacement for the 2600 video game console. A shift towards people wanting to do more than play games meant the next computers, the Atari 800 & 400, had keyboards and the term 'home computers' arrived.

In the early eights there was the crash of the US Video Games industry, where many companies producing video game consoles and home computers in North America either went bankrupt or lost a lot of money. Some of the reasons for this were too much competition, a flood of poor software titles and not enough compatibility between consoles, even ones made by the same manufactures.

It was then in 1984 Atari was sold by Time Warner to Jack Tramiel, who was the founder of Commodore. Atari was restructured selling off old stock at reduced prices to fund a new home computer, which would be called the Atari ST and was released in 1985 [9],[10].

### 2.1.1

# Atari ST Models

The Atari ST was particularly strong in the music industry, with MIDI (Musical Instrument Digital Interface) ports being built in. One of the video modes, being monochrome high resolution (for the time) also meant the Atari ST found its way in DTP (Desktop Publishing) and CAD (Computer Aided Design).

The Atari ST stands for Sixteen/Thirty-two, as it was based around the powerful Motorola MC68000 which had a 16bit external data bus, but internal 32bit registers.

The Atari ST range came in quite a few different flavours [10].

| ST       | Original                                                                     |

|----------|------------------------------------------------------------------------------|

| STM      | RF modulator for TV output                                                   |

| STF      | Internal floppy drive                                                        |

| STFM     | RF Modulator for TV output, internal floppy drive                            |

| STE      | DMA Sound, Blitter chip, enhanced graphics, RF Modulator, internal           |

|          | floppy drive                                                                 |

| Mega ST  | Detachable keyboard, Blitter Chip, internal floppy drive, internal expansion |

|          | bus                                                                          |

| Mega STE | Detachable keyboard, Blitter Chip, internal floppy drive, internal VME       |

|          | expansion bus, optional FPU, 16 MHz CPU with L2 Cache                        |

| Stacy    | Portable Laptop version, internal floppy drive, monochrome 9" LCD            |

|          | screen                                                                       |

Table 1. List of different models Atari produced based around the original ST hardware

# Atari ST Hardware

### 2.2

The original prototype of the Atari ST was built by hand using discrete TTL logic devices using wire wrapping and prototyping printed circuit boards. These were then integrated into four custom ASICs on the production models [11].

Figure 7 - Atari ST CPU Board Prototype

Figure 8 - Atari STfm Motherboard

- 1. Reset circuitry consisting of NE555 monostable

- 2. FPM DRAM, consisting of two banks of 512kbytes

- 3. RF Modulator to convert composite video and audio to RF

- 4. Custom DMA chip

- 5. Western Digital WD1772 Floppy Disk Controller

- 6. Yamaha YM2149 Sound Chip

- 7. Motorola MC68901 MFP

- 8. Motorola MC6850 ACIA one for keyboard interface and another for MIDI

- 9. Custom SHIFTER Video chip inside shielded enclosure

- 10. Bus transceivers to bridge between Data Bus and RAM Data Bus

- 11. Custom GLUE chip

- 12. Motorola MC68000 CPU

- 13. Custom MMU chip

- 14. EPROM's containing TOS (The Operating System)

- 15. Cartridge Port for additional EPROM's

### 2.2.1

### MC68000 CPU

The Atari ST was built around the Motorola 68000 CPU. Some of the MC68000 features are listed below.

- 16 bit data bus

- 24 bit address bus

- Asynchronous bus cycles (to allow for wait states)

- Synchronous bus cycles to interface to older 8 bit 6800 peripherals

- 32 bit internal registers

- 7 Interrupt levels

- Byte, Word and Long data transfers

Listed below are the four custom integrated circuits, which are all closely linked together, and to operate rely on each other.

# 2.2.2

# GLUE

As the name suggests, this IC glues the system together. It is responsible for address decoding and providing chip select lines. It also handles the control of interrupt lines to the CPU, and bus arbitration between CPU and DMA. It also creates the video timing signals.

# 2.2.3

# MMU

This integrated circuit controls the Dynamic RAM signals. It is not as powerful as the name suggests, it doesn't do any memory protection, translation from virtual to physical address or paging. This would be better called a Memory Controller Unit. It multiplexes the CPU address lines to Column and Rows. It also contains a counter for sending video data from RAM to the SHIFTER and also a counter for DMA transfers.

### 2.2.4

### SHIFTER

This integrated circuit takes the data supplied by the MMU and uses a lookup table to display the colour from a palette. All the Atari ST video modes are based on bit planes. There are 3 video modes, 320x200 16 colours (4 bit planes), 320x400 4 colours (2 bit planes) and 640x400 (1 bit plane). The reason for using this method was because the memory bandwidth is not enough to support "chunky" graphic modes where each byte represents a pixel on the screen.

### 2.2.5

### DMA

The DMA (Direct Memory Access) controller is responsible for transferring chunks of data between the RAM and DMA port, which is used for connection of hard drives. It also resizes the 16 bit data bus to the external 8 bit bus featured on the DMA port. It is also used to carry out DMA transfers to and from the Western Digital WD1772 FDC (Floppy disk controller).

### 2.2.6

### MFP

The MFP is a MC68901 manufactured by Motorola and is an abbreviation for Multi Function Peripheral Chip. In the Atari ST it is used to provide a RS232 serial port. It also serves as an interrupt controller, allowing more interrupt sources than the Motorola MC68000 CPU provides. It also contains four universal timers.

### 2.2.7

### YM2149

The YM2149 is manufactured by Yamaha and is primarily the sound generator. It contains 3 independent tone generators. It also has two general purpose 8 bit data ports. In the Atari ST these are used for the Centronics printer interface and the other is used to help control the floppy disk and RS232 hardware flow control.

#### 2.2.8

### ACIA

The ACIA is an abbreviation for Asynchronous Communications Interface Adapter. The Atari ST contains two MC6850. Their task is to serialize data to communicate with the Keyboard and MIDI devices. They were designed as a peripheral chip to the MC6800 processor, and so they only feature an 8 bit wide bus and use the legacy synchronous bus that the MC68000 CPU can offer.

### 2.2.9

### FDC

The FDC is an abbreviation for Floppy Disk Controller. It is a WD1772 made by Western Digital. It is connected to the DMA chip so that all transfers are via DMA relieving the CPU from disk transfers. It contains the logic for precise timing of the floppy disk drive heads and motors and sterilization of data.

# Atari ST Operating System

After the hardware came close to being completed an operating system was needed. Atari decided to use a new operating system with a GUI (Graphical User Interface) from Digital Research, providing a WIMP (Windows, Icons, Menu, Pointing Device) environment, much like the Apple Macintosh. This was essentially a port from the Intel 8088 version they had developed for the IBM compatible machines. The operating system was called TOS (The Operating System), and provided the programmer with many system calls by using the TRAP software exception calls. In TOS there are three layers, called the BIOS, XBIOS and GEMDOS. The BIOS and XBIOS are hardware dependant, while the GEMDOS layer is hardware independent. The operating system on very early Atari ST models came on floppy disk, but the more common later versions placed this operating system on PROM memory devices [12].

With this project being mainly hardware based only the low level parts of the operating system, and particularly how the operating system starts up and boot straps.

#### 2.3.1

#### Atari ST Boot Up Operation

The Motorola 68000 on boot up requires initial values to load into its supervisor stack pointer and reset vector address. These come in the form of two long words at address 0x000000 to 0x000007.

Figure 9 shows the path the operating system takes on boot up. It was drawn from the reverse engineered commented source code [13],[14].

Figure 9 - Atari ST boot up sequence

Boot up sequence

(1)

- Load SSP with long word value from 0xFC0000.

- Load PC with long word value from 0xFC0004 (Garbage value, memory not yet sized).

- CPU Supervisor Mode Interrupts disabled (IPL=7).

- RESET instruction to reset all peripheral chips.

- Check for magic number 0xFA52235F on cartridge port, if present jump to diagnostic cartridge.

(2).

Test for warm start, if memvalid (0x000420) and memval2 (0x00043A) contain the Magic numbers 0x7520191F3 and 0x237698AA respectively, then load the memconf (0xFF8001) contents with data from memctrl (0x000424).

(3)

If the resvalid (0x000426) contains the Magic number 0x31415926, jump to reset vector taken from Resvector (0x00042A).

(4)

- YM2149 sound chip initialized (Floppy deselected).

- The vertical synchronization frequency in syncmode (0xFF820A) is adjusted to 50Hz or 60Hz depending on region.

- Shifter palette initialized.

- Shifter Base register (0xFF8201 and 0xFF8203) are initialized to 0x010000.

- The following steps 5 to 8 are only done on a coldstart to initialize memory.

(5)

Write 0x000a (2 Mbyte & 2 Mbyte) to the MMU Memory Configuration Register 0xff8001).

(6)

- Write Pattern to 0x000000 0x0001ff.

- Read Pattern from 0x000200 0x0003ff.

- If Match then Bank0 contains 128 Kbyte; goto step 7.

- Read Pattern from 0x000400 0x0005ff.

- If Match then Bank0 contains 512 Kbyte; goto step 7.

- Read Pattern from 0x000000 0x0001ff.

- If Match then Bank0 contains 2 Mbyte; goto step 7.

- panic: RAM error in Bank0.

# (7)

- Write Pattern to 0x200000 0x2001ff.

- Read Pattern from 0x200200 0x2003ff.

- If Match then Bank1 contains 128 Kbyte; goto step 8.

- Read Pattern from 0x200400 0x2005ff.

- If Match then Bank1 contains 512 Kbyte; goto step 8.

- Read Pattern from 0x200000 0x2001ff.

- If Match then Bank1 contains 2 Mbyte; goto step 8.

- note: Bank1 not fitted.

- (8)

- Write Configuration to MMU Memory Configuration Register (0xff8001).

- Note Total Memory Size (Top of RAM) for future reference in phystop (0x00042E).

- Set magic values in memvalid (0x000420) and memval2 (0x00043A).

(9)

- Clear the first 64 Kbytes of RAM from top of operating system variables (0x00093A) to Shifter base address (0x010000).

- Initialize operating system variables.

- Change and locate Shifter Base register to 32768 bytes from top of physical ram.

- Initialize interrupt CPU vector table.

- Initialize BIOS.

- Initialize MFP.

(10)

• Cartridge port checked, if software with bit 2 set in CA\_INIT then start.

(11)

Identify type of monitor attached for mode of operation for the Shifter video chip and initialize.

(12)

Cartridge port checked, if software with CA\_INIT clear (execute prior to display memory and interrupt vector initialization) then start.

(13)

• CPU Interrupt level (IPL) lowered to 3 (HBlank interrupts remain masked).

(14)

Cartridge port checked, if software with bit 1 set in CA\_INIT (Execute prior to GEMDOS initialization) then start.

(15)

• The GEMDOS Initialization routines are completed.

(16)

- Attempt boot from floppy disk if operating system variable \_bootdev (0x000446) smaller than 2 (for floppy disks) is. Before a boot attempt is made bit 3 in CA\_INIT (Execute prior to boot disk) checked, if set, start cartridge.

- The ACSI Bus is examined for devices, if successful search and load boot sector.

• If system variable \_cmdload (0x000482) is 0x0000, skip step 17.

(17)

- Turn screen cursor on

- Start any program in AUTO folder of boot device

- Start COMMAND.PRG for a shell

(18)

- Start any program in AUTO folder of boot device

- AES (in the ROM) starts.

# **Chapter 3**

# Research

# 3.1

# FPGA

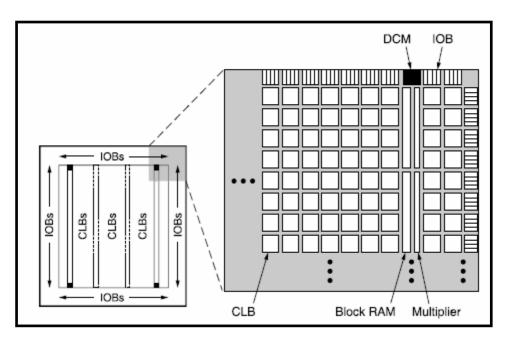

An FPGA is a programmable logic device, with the configuration being volatile. The FPGA contains many complex logic blocks that have interconnects running between them in a grid like fashion. There are also dedicated interconnects like global clock lines. The configuration is often programmed in a high level HDL (Hardware descriptive Language) like Verilog or VHDL, or sometimes as a schematic. The majority of modern FPGAs contain embedded functions, such as adders, multipliers, memory, digital PLLs and even DSP cores. There has been a recent trend in pushing soft core processors into designs for FPGA creating complete systems on chip that can be fine tuned for specific tasks [15].

Figure 10 –Xilinx FPGA block layout

# **Base Hardware**

The design is to be based around a Xilinx FPGAs, as there are special free versions of the IDE (Integrated Development Environment) which are only slightly limited from the commercial versions. The type of Xilinx fitted to the board needs to be large enough (in terms of logic elements) to fit the whole project, which is not something that can be estimated easily. The Atari ST is based on a 5 volt logic platform, and so having some 5 volt capabilities on the chosen development board will be a real bonus.

| Board                | FPGA      | I/O's       | Notes           | Price            |

|----------------------|-----------|-------------|-----------------|------------------|

| Xilinx Spartan-3     | XC3S200   | 100         | Programming     | £80 plus         |

| Starter Kit          |           |             | Cable, PS/2     | shipping and     |

|                      |           |             | ports, VGA      | customs          |

| Enterpoint           | XC3S1500  | 120 plus 50 | Programming     | £120 inc         |

| Raggedstone          |           | 5v tolerant | Cable, 7        | shipping         |

|                      |           | on PCI      | segment display | (special student |

|                      |           | header      |                 | price)           |

| Inrevium TB-3S-      | XC3S1400A | 128         | 4Mbyte DDR      | £650 plus        |

| 1400A-IMG            |           |             | SDRAM,          | shipping and     |

|                      |           |             | RS232           | customs          |

| Philips PXPDKSP3     | XC3S1000  | 80          | PCI Express     | £700 plus        |

|                      |           |             | Bridge,         | shipping and     |

|                      |           |             | Prototype Area. | customs          |

| Digilent Inc. Nexys- | XC3S500E  | 59          | Programming     | £50 plus         |

| 2                    |           |             | Cable, ps2      | shipping and     |

|                      |           |             | ports, vga,     | customs          |

|                      |           |             | SDRAM           |                  |

Table 2 - Comparison of some of the available Xilinx development boards

### 3.2

### **IP** Cores

IP Core stands for Intellectual Property Core. They are a block of logic as an element to design reuse, a trend towards repeated use of previously designed components. IP cores may be licensed to another party or can also be owned and used by a single party alone. Some cores are only offered as netlists, to protect the vendor against reverse-engineering. Others are offered as synthesizable cores in hardware descriptive languages like Verilog or VHDL [16].

There are already a couple of projects for putting an Atari ST inside an FPGA, thankfully both in the VHDL language. There is MikeJ's project, although only the source to his YM2149 Sound Chip is available. There is also Wolfgang Forester's project, which includes an IP Core of every Atari ST semiconductor.

### 3.4

#### **Software Suite**

The Xilinx IDE comes in two flavours, ISE Foundation and ISE Webpack where the latter is a free version. The free ISE WebPack is only restricted in the devices it supports, and that is generally the newest or largest devices like the Virtex 5 SXT family [17]. There are a range of tools included like Simulators, Timing Analysers and Power Analysis. There are additional options that can be bought for some of the more advanced features like ChipScope (FPGA probe) and Modelsim (Powerful Simulator).

### 3.5

#### Processor

The processor can either be an IP Core or real genuine Motorola (now Freescale) 68000. At the time of writing no free 68000 IP Core is available that has been tested and verified. There are a few different incarnations of the 68000 to help keep it up to date as production has spanned almost 30 years now [18].

#### 3.3

| Model    | Technology | Voltage | Details                                             | Manufactured |

|----------|------------|---------|-----------------------------------------------------|--------------|

| 68000    | NMOS       | 5v      | Original                                            | No           |

| 68HC000  | CMOS       | 5v      | Low Power                                           | Yes          |

| 68HC001  | CMOS       | 5v      | Low Power, 8/16bit data<br>bus                      | Yes          |

| 68EC000  | CMOS       | 5v      | Embedded version, 8/16bit data bus                  | No           |

| 68SEC000 | CMOS       | 3.3v    | Embedded version, 8/16bit<br>data bus, static clock | Yes          |

| 68008    | NMOS       | 5v      | 8bit data bus, 20/22bit<br>address bus              | No           |

| 68010    | NMOS       | 5v      | Virtual machine & virtual memory instructions       | No           |

Table 3 - Comparison of 68000 family processors

### 3.6

# **Books and literature**

- Atari ST Internals ISBN : 0-916439-46-1

- Atari ST Profibuch ISBN : 3-88745-563-0

- 68000 Microsystems Design ISBN : 0-534-94822-7

- MC68000 Hardware Datasheet

- MC68000 Programmers Reference Manual

# Debugging

There are many ways to debug and fault find hardware. These range from the very basic up to monitoring registers in a CPU and data flow.

A set of LEDs can be used to check that an FPGA has been programmed correctly. By using a clock signal and diving it down to a signal of a one or two Hz this can be used to drive an LED and make it flash. Another use of LEDs is to show the status of signals, like a reset line or processor state. They are very often the first thing to get working when starting on a new development board.

A 7 segment display can be used much in the same way as a single LED but allowing display of whole bytes, words of even long words if enough segments are available. A bit more functionality is need in an FPGA to achieve this as quite often 7 segment displays need to be scanned one segment at a time at a fast enough rate for the eye not to see any flicker.

Single Stepping is a way of stepping through the boot up code of a board, one instruction at a time. It will usually be used in combination with a method to display bus signals to verify or diagnose a problem with the board. Using this method needs hardware than can support halting the system.

Xilinx Chipscope and Altera SignalTap are pieces of software to view any internal signal of an FPGA. They manage this by using the JTAG interface and modifying the FPGA bitstream with some additional logic.

A Monitor program is a utility that is loaded from ROM into an available processor. It is designed to use little or no resources so it can run when some hardware isn't fully functioning. It usually communicates over a simple RS232 implementation and allows

### 3.7

the user to write small assembling programs. These can be used to test various parts of a system.

### 3.8

### **Operating System Versions and storage**

The operating system for the Atari ST went through various versions from TOS 1.00 to TOS 2.06 [19].

| Version | Date                           | Computer     | Details                        |

|---------|--------------------------------|--------------|--------------------------------|

| 1.00    | 20 <sup>th</sup> November 1985 | ST           | Original Version               |

| 1.02    | 22 <sup>nd</sup> April 1987    | ST, Mega ST  | Mega ST Blitter & RTC support  |

| 1.04    | 6 <sup>th</sup> April 1989     | ST, Mega ST, | Bug Fixes, faster disk I/O     |

|         |                                | Stacy        |                                |

| 1.60    | Unknown                        | STE          | Support for STE hardware       |

| 1.62    | 1 <sup>st</sup> January 1990   | STE          | Bug Fixes                      |

| 2.05    | Unknown                        | Mega STE     | Support for Mega STE hardware  |

| 2.06    | 14 <sup>th</sup> November 1991 | Mega STE     | Features added to GUI, support |

|         |                                |              | for all ST range               |

Table 4 - Comparison of different TOS versions

The Operating System on the Atari ST is stored in PROMs which are rather out dated these days and not ideal for early stages of design. Non Volatile Flash memory is now the norm and is being used as a replacement to PROM, many of the FPGA development boards contain some Flash memory.

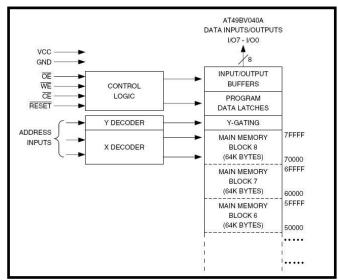

Figure 11 – Flash memory organisation

Reading from Flash is the same as a PROM, but writing to Flash takes a little more work. Before writing to Flash memory command sequences need to be issued. Also the data in the flash is organised into Blocks as shown in figure x.

From the Atmel data sheet for the AT49BV040A 4-megabit flash memory chip it's also worth noting that it is not possible to write bits that are currently 0s back to 1s, only erase commands can do that. Below is the list of commands that the Atmel Flash memory uses.

- Read

- Full Chip erase

- Sector erase (block erase)

- Byte program (Write byte)

- Boot block lockout

- Product ID entry

- Product ID Exit

# 3.9

### System memory

There are many types of RAM available, but they can be split into two types depending on the technology used to store the data. Dynamic RAM uses capacitance to store a charge representing a bit of data, therefore it needs to be refreshed periodically. Static RAM uses flip flops, and thus need more logic per data bit of storage [20].

Fast Page Mode (FPM) DRAM is the type of memory fitted to the Atari ST. A row address only needs to be sent once, for many accesses to adjacent memory locations. They are only commonly available in 5v and usually come in a package called a SIMM with either 30 or 72 pins providing 8 bits or 32 bits respectively.

EDO DRAM is essentially the same as FPM, except that the timing has altered slightly for a small access time improvement. They are available in 5v and 3.3v and usually come packaged in a 32 bit wide 72 pin SIMM.

Synchronous Dynamic RAM (SDRAM) was the first type of synchronous ram, spawning many newer types like Double Data Rate (DDR) SDRAM. Data transfers are synchronised to the system clock. To access the SDRAM commands are issued to be executed. Due to their command structure and high clock speed (66Mhz and above) they are inherently more difficult to interface to. They are available in 5v and more commonly 3.3v and usually come packaged in a 64 bit wide 168 pin DIMM.

Static RAM (SRAM) is quite different from dynamic memory. Rather than using capacitors to hold a charge to represent a state of a bit it uses flip flops. This also means that it does not need the usual periodic refresh that dynamic RAM needs. It is also addressed by its full address width in one transaction, the column and row decoding is done internally. The disadvantage of static RAM is the cost. It is generally faster than dynamic RAM and so is often used for cache memory.

### 3.10

#### Serial Port

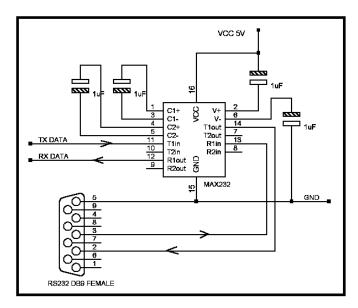

An RS232 serial port can have many uses from debugging, transferring data from a host computer and communications. In the Atari ST it was primarily used for communications with Modem's. Interfacing a serial port to an FPGA is quite simple, the voltage levels of RS232 swing from -12 to +12v so a voltage level translator is needed like a Maxim MAX232. The software overheads are very small which is why serial is still favoured over USB and other communication buses. Serial Ports can be implemented by only three wires, ground, transmit and receive.

### Video Output

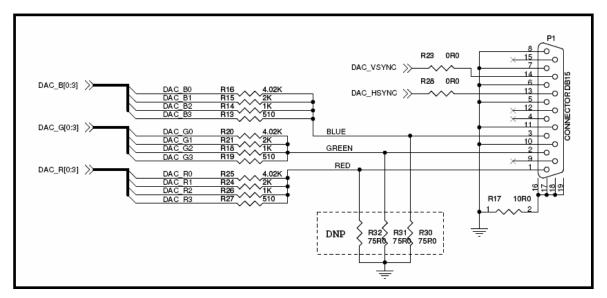

Conversions for video from digital to analogue are usually done by one of two methods, a specialist Video DAC or an inexpensive resistor ladder. An example of the resistor ladder was found in the schematics of the Xilinx Spartan 3A start kit.

Figure 12 – Digital to Analogue using resistor ladders

The resistor ladder is easy to implement and is inexpensive but suffers from bad picture quality especially when used at higher resolutions, requiring higher video bandwidth. The resistors used in the schematic above are non standard values that appear in the E48 and onwards range of resistor values. They need to be of good quality and high degree of tolerance, but are still susceptible to drifting in value with temperature. The video intensity will also change depending on the load that the resistor ladders are driving into.

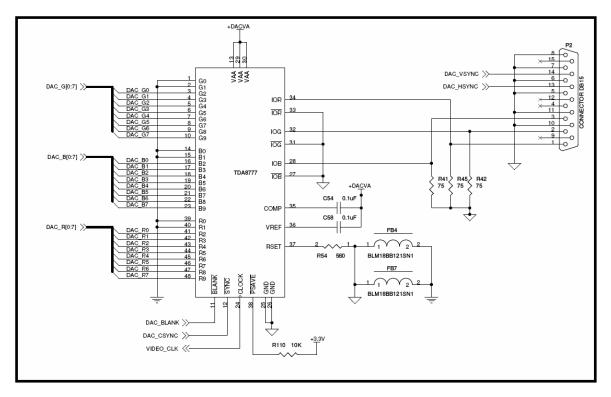

An example of a Video DAC was found in the schematics of the Xilinx Spartan-3 PCI Express Starter Kit. It uses a Philips TDA8777 Video DAC and although requires little external circuitry, it does cost more than the resistor ladder. It has a maximum conversion frequency of 330 MHz. It also helps to protect the FPGA from possible electrical damage, as it is bad practice to use non buffered FPGA signals onto external ports or connectors.

### 3.11

Figure 13 – Digital to Analogue using specialised DAC

# Chapter 4

# Design

# 4.1

# Components

This section describes the components chosen and how they will interconnect with each other. The components chosen have been based on the previous research and on availability.

# 4.1.1

# **Base Hardware**

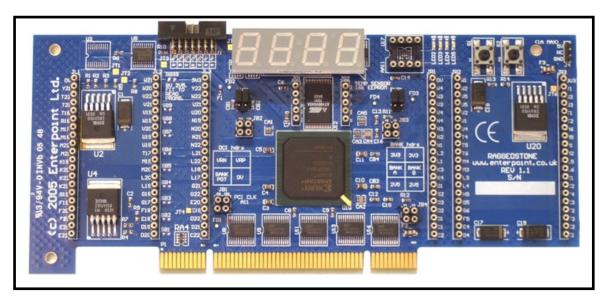

It has been decided to use the Enterpoint RaggedStone development board. Their reduced student price, large FPGA, and plentiful I/O including optional 5v I/O header will be ideal. The RaggedStone was also designed to accept plug in daughterboard modules, one on each end of the board.

Figure 14 – Enterpoint RaggedStone FPGA development board

The board has the following features:

- 4 Digit 7 Segment Display

- 4Mbit Flash memory (524288 x 8) Atmel AT49BV040A

- 16k Serial EEPROM

- Temperature Sensor

- Oscillator Socket

- 4 LED's and 2 momentary push switches

- Voltage selectors for modules and associated FPGA bank (3.3v and 2.5v)

- Self resetting Poly fuses

### 4.1.2

### Processor

The CPU chosen is the MC68SEC000, purely because it is the only version that is 3.3v. It is object-code compatible with the MC68000 but not entirely hardware compatible.

Bus Arbitration (a method for allowing other devices on the system bus to take control) is handled with a 2 wire protocol, instead of the original overly complex 3 wire protocol. The differences are covered in depth in the MC68000 datasheet.

The MODE pin selects 8 or 16 bit data bus operation, and is sampled at reset.

Support for legacy MC6800 synchronous peripherals has been completely removed. The missing signals are the E Clock,  $\overline{VPA}$  (Valid Peripheral Address) and  $\overline{VMA}$  (Valid Memory Address). A VHDL component will replicate these signals, creating a synchronous bus from the more commonly used asynchronous MC68000 bus [21].

The processor will fit onto a daughterboard installed on the RHS (Right Hand Side) I/O pins. One of the momentary push switches will act as the system reset.

### 4.1.3

#### System memory

The memory chosen is SRAM (Static RAM), because it simplifies a design and is available in a variety of voltages. The ability to use it without refreshing means it is great for prototypes or in debugging situations, as the whole design can be halted without loosing the contents of the memory.

The memory will fit onto a daughterboard installed on the LHS (Left Hand Side) I/O pins.

Using SRAM for the memory will be transparent to the user and all software, and will not create any problems.

### 4.1.4

### Debugging

The following features will aid in debugging the system

A 7 segment display will show the current status of the CPU data and address bus. As the display can only show a maximum of 4 hexadecimal characters, the display will scroll.

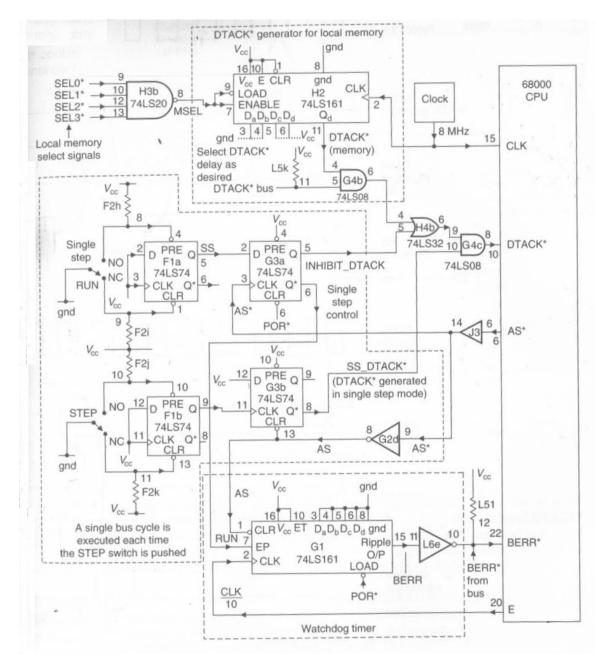

One of the onboard switches will be used to step through the operating system. This will be achieved by intercepting  $\overrightarrow{\text{DTACK}}$  and  $\overrightarrow{\text{BERR}}$  bus cycle termination signals. This is an interpretation of the design from Microprocessor Systems Design by Alan Clements.

The four onboard LED's will be used to show the status of the CPU or other parts of the design. One useful signal is  $\overrightarrow{HALT}$  which the CPU drives when it has encountered a situation from which it can't recover. In this state it drives all its pins to high impedance.

A set of 5 header pins will be dedicated as points to connect a dual channel oscilloscope. This will assist in finding timings errors, phase and cycle time of clock signals and general verification.

### 4.1.5

#### **Operating System Versions and storage**

TOS 1.00 has been chosen as the initial Operating System to use. Although is suffers from many bugs, the BIOS has been listed and fully commented in the book "Atari ST Internals" by Data Becker. Combined with the ability to single step through each instruction will undoubtedly help finding any problems in the design.

The operating system will be stored in the Flash memory that is part of the RaggedStone development board. The Flash memory data bus is only 8 bits wide, therefore it will be necessary to design a VHDL component to wrap around the Flash memory and resize the data bus to 16 bit that the Atari ST uses.

There also needs to be a way to load the Operating System into the Flash memory. As the Flash memory is non-volatile once this has been programmed, the contents remain even after power is removed. Xilinx have created for their own Spartan development board an FPGA design that uses the RS232 serial port to receive data from a host computer and load into the Flash memory. Their design is based around the PicoBlaze system on chip and using the ST Microelectronics M29DW323DT Flash memory chip [22].

## 4.1.6

## 5v PCI I/O

The 5v tolerant I/O will be attached to a custom PCB at the rear of the enclosure for the following use:

- VGA interface port

- Floppy Disk Drive port

- RS232 Serial port

- Keyboard/Mouse interface

## 4.1.7

## VGA

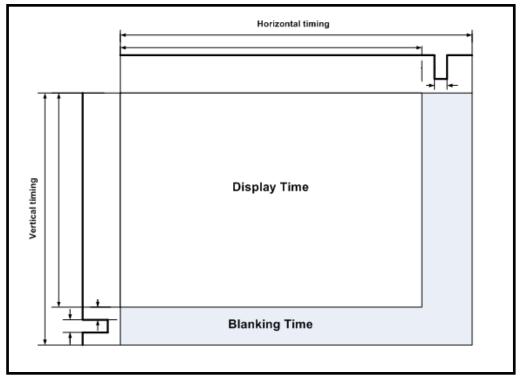

VGA is a mix of analogue and digital. The colour intensity is carried over three analogue signals for Red Green and Blue. The horizontal and vertical synchronisation signals are digital 5v.

Figure 15 – VGA video timing

The Atari ST can display colours from a palette of 4096 different colours. Therefore each colour component can have 2<sup>4</sup> levels of intensity. To convert from the digital output from an FPGA to the analogue input of a VGA monitor, a DAC (Digital to Analogue) converter will be used.

## 4.1.8

## Floppy Disk Drive

The floppy drive requires a minimum of 11 signals to function. In the Atari ST these were the following, with reference to the pin number on the 34 pin 0.1" pitch IDC header [23].

## To Floppy Drive

- 10: Drive Select

- 16: Motor On

- 18: Step Direction When you step the head, this line must tell the drive whether to step in or out.

- 20: Step. This line is briefly signaled to step the drive one track in the direction step direction specifies (in or out).

- 22: Write Data. This is a bit stream data for the disk track at around 100,000 baud.

- 24: Read/Write. When +5, the drive is reading. When +0, the drive is writing.

- 32: Side Select. Pull to +0 volts to write to back side of diskette.

## From Floppy Drive

- 8: Index Pulse. Goes to ground briefly each rotation, five times per second (300 RPM). Otherwise +5.

- 26: Track 0. +5 unless drive is at track 0, when this pin goes to +0 volts. This is how the drive tells the FDC to stop stepping it towards track 0.

- 28: Write Protect. +0 volts if the write protect tab is set on the diskette; +5 volts if it is okay to write to the diskette.

• 30: Read Data: This is the bit stream data from the track, at 100,000 baud, complete with wow and flutter.

The floppy drive used in the Atari ST was in fact the same as used in many IBM Clone PCs. The Atari ST from TOS v1.02 onwards even uses the FAT12 filing system, compatible with a PC formatted disk.

#### 4.1.9

#### **RS232 Serial**

The RS232 will serve two purposes. Firstly it is used as an interface to a host computer to transfer the operating system into the Flash Memory. Secondly, it will be used for the Atari ST serial port. The more common 9 pin female D-Type connector will be used, instead of the Atari ST 25pin D-Type connector. Flow control and specialist MODEM only signals will be omitted to reduce the number of FPGA I/Os needed from 9 down to only 2.

Figure 16 – RS232 to TTL level translator

|                     | 9-Pin | 25-Pin |

|---------------------|-------|--------|

| Carrier Detect      | 1     | 8      |

| Receive Data        | 2     | 3      |

| Transmit Data       | 3     | 2      |

| Data Terminal Ready | 4     | 20     |

| System Ground       | 5     | 7      |

| Data Set Ready      | 6     | 6      |

| Request to Send     | 7     | 4      |

| Clear to Send       | 8     | 5      |

| Ring Indicator      | 9     | 22     |

*Table 5 – Serial port pin description*

## 4.1.10 Keyboard and Mouse

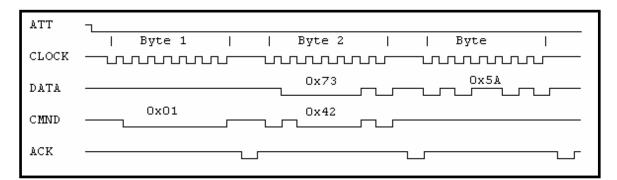

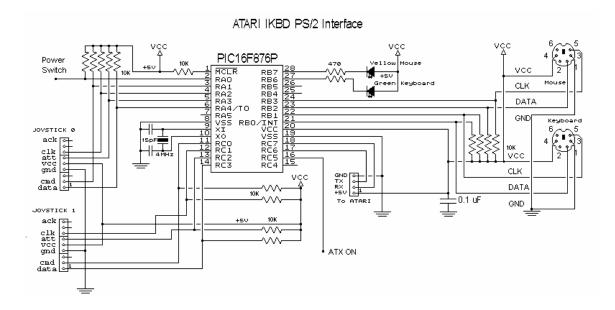

The Atari ST communicates to the keyboard via a simple serial interface. The original keyboard contains a small Hitachi microcontroller that scans the keyboard matrix and the status of the mouse and joysticks. It then creates packets of data to be sent over the serial connection to the MC6850 UART on the Atari ST motherboard. The Atari keyboard and mouse contain mechanical components, and are one of the first parts to break or become faulty. For this reason it has been decided to implement a conversion from PC PS2 keyboard and mouse protocol. A project called 'Eiffel' by Laurent Favard, and later Didier Méquignon does just that, using an inexpensive PIC Microcontroller [24].

#### 4.2

#### Other differences between the original Atari ST and the design

The Atari ST as mentioned previously has 3 different resolutions. The monochrome high resolution has vertical and horizontal timings that are close to the VGA specification. The Low and Medium colour resolutions, which were designed to be displayed on a television, do not meet the VGA timing specification. The problem arises from the slow pixel clock, resulting in a horizontal synchronisation frequency of 15 KHz, which is half of VGA timing. To use the Atari ST in all three resolutions it meant you either need to have both a television and high resolution monitor, or a very expensive 'Multisync' monitor. To overcome this, a device known as a 'scan doubler' will be designed to buffer the RGB data and resynchronise it to a higher pixel clock.

The Atari ST didn't have the facility for an internal hard drive, to keep the costs low. However, a DMA port was available for connecting to external hard drives. The Atari ST was designed just before the SCSI (Small Computer System Interface) command protocol was finalised, and thus Atari used the ACSI (Atari Computer System Interface) command protocol. As the IDE (Integrated Disk Electronics) hard drives became popular on IBM PC Clones, their price dropped compared to the SCSI equivalent. Atari realized that and on their last home computers, the Falcon and Stacy, they added IDE support.

The design will use a simple IDE interface, to use a Compact Flash card in IDE mode as they are 3.3v tolerant which enables direct linking to the Xilinx FPGA. As an IDE interface is to be designed, the original ACSI port will be left out of the design [25].

The Atari ST featured a port for a cartridge, sometimes known as the ROM port. As the name suggests this is a read only direct connection to the CPU data and address bus. The design will not include this, as although easy to implement in logic, the required 2mm pitch edge connector is not available. It is also not needed for the Atari ST to function, it rarely used for software protection dongles and most recently Ethernet and USB interfaces.

The MIDI ports are only use by music sequencing software and are not an essential part of the Atari ST design. They are based around the same UART that the keyboard uses. MIDI uses a current loop, where the current, not the voltage level defines the logic state. Therefore, MIDI ports require quite a bit of additional external circuitry.

The external 2<sup>nd</sup> floppy drive port will not be implemented as no software requires two drives. The only case where one may be useful is duplicating floppy disks, but the majority of floppy disk copying software use the system RAM as temporary storage of files.

The design will be built into a standard Micro ATX enclosure. This will provide physical protection for the delicate electronics and

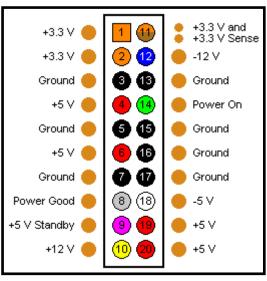

Figure 17 – ATX pin description

allow use of an ATX power supply. The ATX power supply provides a wide range of voltages. One in particular, the +5v Standby can be used to provide power to additional circuitry on a motherboard. This is used to support soft-off or standby and can be used for remote wake up through Wake-on-Ring or Wake-on-LAN. It has been chosen that the 'Eiffel' Keyboard and Mouse microcontroller will be powered from this +5v standby voltage and use modified firmware to control the ATX power supply. This allows the Power On key on many extended PS2 keyboards to turn on the computer.

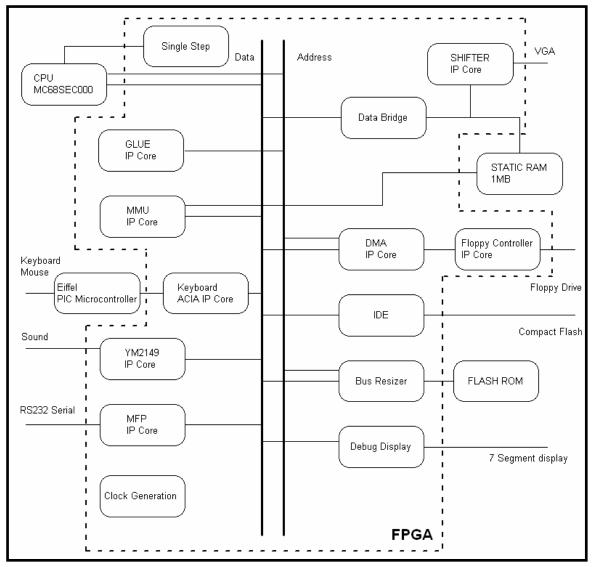

Figure 18 – Design Block diagram

To summarise, the design will follow the original Atari ST, but make use of more common and readily available components from IBM PC Clones.

## 4.3 Process of Implementation

The implementation will be created in stages, logically from a small system with minimal IP Cores to the final version. Below is a brief proposal of stages involved. The order may change during implementation due to certain stages requiring later parts of the design.

- A simple LED Flash

- Verify Video Digital to Analogue works

- A project to transfer Operating System into Flash memory

- Test reading from Flash memory

- A new project with support logic, reset and clock generation

- A debug control and display

- Add Glue IP Core and verify

- Add MMU IP Core, SRAM memory and verify

- Add Shifter IP Core and verify

- Add MFP IP Core and verify

- Add Yamaha IP Core and verify

- Add Keyboard/Mouse ACIA IP Core

- Add Eiffel interface and verify

- Add DMA IP Core and verify

- Add FDC IP Core and verify

# **Chapter 5**

# Implementation

## 5.1

## **Flashing LED**

The first task was to make sure that the oscillator clock works and that the JTAG programming works. To do this a simple LED flash routine was written. However, before this was done, constraints for the I/O pin mapping and a top level component needed to be written. This was done by looking at the schematics of the RaggedStone development board and laboriously assigning names for each I/O pin. Appendix A lists the constraints file and component file.

Shown right was the VHDL architecture for flashing an LED at approximately 1Hz using a 32MHz oscillator clock.

Figure 19 – Architecture for LED Flash

5.2

## VGA Colour pattern

The next step was to implement a Digital to Analogue Converter (DAC) for the Red, Green and Blue signals to drive the VGA port. The converter being used was an ST Microelectronics STV8438, which is capable of 3 x 8bit colour. As the Atari ST can only produce 3 x 4bit colour, the MSB (Most Significant Bits) are used and the rest are tied low. Appendix B shows the schematic.

To drive the VGA monitor a colour pattern generator was discovered written by MikeJ [26]. The colour pattern generator was designed for the Xilinx Spartan-3E Starter Kit

development board, so using the project on the Raggedstone will not work as the pin constraints are wrong. To rectify this, the top level of the project was instantiated as a component using the same constraints from the previous LED Flasher stage.

Another change that needed to be made was to exchange the 32 MHz oscillator for a 50 MHz oscillator as mentioned in the comments in the colour pattern generator project. If this isn't changed the signals will not adhere to the VGA specification and a monitor will unlikely be able to 'sync' to the reduced frequencies.

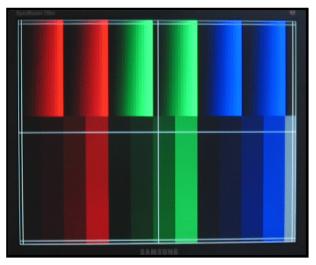

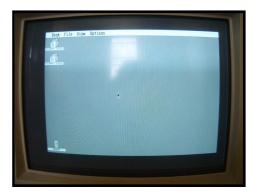

*Figure 20 – Colour test display*

Once the project was built a colourful test pattern was displayed on an attached VGA monitor. This verifies that the video DAC was functioning correctly and the conversion from 3.3v to 5v works well, even for high speed digital signals.

## 5.3

#### Writing bytes to Flash Memory

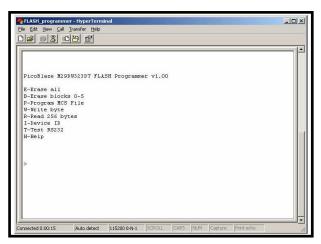

Next on the list was to load data into the RaggedStone onboard Flash memory. A design was found on the Xilinx website for the Spartan-3A/3AN Development Starter Kit. This design was intended to be used with the ST Microelectronics M29DW323DT Flash memory that was featured on the Xilinx Spartan-3A/3AN development board. It Figure 20 – Flash Programmer menu Xilinx Picoblaze embedded the

uses

microcontroller, and by using a simple terminal program over an RS232 serial connection you can manually program individual bytes, download complete files, erase the flash, read the memory to verify contents, and display the Flash memory device identifier and 64-bit unique device numbers.

An RS232 serial port was added as mentioned in the Design. (Paragraph 4.1.9)

After building the project for the RaggedStone board, it became apparent that it didn't work. The menu choices were available proving the serial connection worked fine but programming a single byte didn't work, let alone the entire Flash memory space. The only real difference between the Xilinx Spartan-3A/3AN development board and the RaggedStone was the type of Flash memory device. The RaggedStone uses an Atmel AT49BV040A and the Xilinx board uses an ST Microelectronics M29DW323DT, both configured as 8 bit wide data bus. The difference becomes quite clear when reading the data sheets provided by the manufacturers.

#### Atmel AT49BV040A

| Command                           | Bus    | 1st<br>Cy |                  | 2nd I<br>Cyc       |      | 3rd<br>Cy | Bus<br>cle | 4th<br>Cy |                 | 5th<br>Cy |      | 6th<br>Cy         | Bus<br>cle |

|-----------------------------------|--------|-----------|------------------|--------------------|------|-----------|------------|-----------|-----------------|-----------|------|-------------------|------------|

| Sequence                          | Cycles | Addr      | Data             | Addr               | Data | Addr      | Data       | Addr      | Data            | Addr      | Data | Addr              | Data       |

| Read                              | 1      | Addr      | D <sub>OUT</sub> |                    |      |           |            |           |                 |           |      |                   |            |

| Chip Erase                        | 6      | 555       | AA               | AAA <sup>(2)</sup> | 55   | 555       | 80         | 555       | AA              | AAA       | 55   | 555               | 10         |

| Sector Erase                      | 6      | 555       | AA               | AAA                | 55   | 555       | 80         | 555       | AA              | AAA       | 55   | SA <sup>(5)</sup> | 30         |

| Byte Program                      | 4      | 555       | AA               | AAA                | 55   | 555       | A0         | Addr      | D <sub>IN</sub> |           |      |                   |            |

| Boot Block Lockout <sup>(3)</sup> | 6      | 555       | AA               | AAA                | 55   | 555       | 80         | 555       | AA              | AAA       | 55   | 555               | 40         |

| Product ID Entry                  | 3      | 555       | AA               | AAA                | 55   | 555       | 90         |           |                 |           |      |                   |            |

| Product ID Exit <sup>(4)</sup>    | 3      | 555       | AA               | AAA                | 55   | 555       | F0         |           |                 |           |      |                   |            |

| Product ID Exit <sup>(4)</sup>    | 1      | XXX       | F0               |                    |      |           |            |           |                 |           |      |                   |            |

|                        | £      |     |      |     |      | Bus V        | Write O | peratio | ns   |     |      |     |      |

|------------------------|--------|-----|------|-----|------|--------------|---------|---------|------|-----|------|-----|------|

| Command                | ength. | 1   | st   | 2nd |      | 3rd          |         | 4th     |      | 5th |      | 6th |      |

|                        | Ľ      | Add | Data | Add | Data | Add          | Data    | Add     | Data | Add | Data | Add | Data |

| Read/Reset             | 1      | Х   | F0   |     |      |              |         |         |      |     |      |     |      |

| Read/Reset             | 3      | AAA | AA   | 555 | 55   | Х            | F0      |         |      |     |      |     |      |

| Auto Select            | 3      | AAA | AA   | 555 | 55   | (BKA)<br>AAA | 90      |         |      |     |      |     |      |

| Program                | 4      | AAA | AA   | 555 | 55   | AAA          | A0      | PA      | PD   |     |      |     |      |

| Quadruple Byte Program | 5      | AAA | 55   | PA0 | PD0  | PA1          | PD1     | PA2     | PD2  | PA3 | PD3  |     |      |

| Unlock Bypass          | 3      | AAA | AA   | 555 | 55   | AAA          | 20      |         |      |     |      |     |      |

| Unlock Bypass Program  | 2      | Х   | A0   | PA  | PD   |              |         |         |      |     |      |     |      |

| Unlock Bypass Reset    | 2      | Х   | 90   | Х   | 00   |              |         |         |      |     |      |     |      |

| Chip Erase             | 6      | AAA | AA   | 555 | 55   | AAA          | 80      | AAA     | AA   | 555 | 55   | AAA | 10   |

| Block Erase            | 6+     | AAA | AA   | 555 | 55   | AAA          | 80      | AAA     | AA   | 555 | 55   | BA  | 30   |

| Erase Suspend          | 1      | BKA | B0   |     |      |              |         |         |      |     |      |     |      |

| Erase Resume           | 1      | BKA | 30   |     |      |              |         |         |      |     |      |     |      |

| Read CFI Query         | 1      | AA  | 98   |     |      |              |         |         |      |     |      |     |      |

| Enter Extended Block   | 3      | AAA | AA   | 555 | 55   | AAA          | 88      |         |      |     |      |     |      |

| Exit Extended Block    | 4      | AAA | AA   | 555 | 55   | AAA          | 90      | Х       | 00   |     |      |     |      |

#### ST Microelectronics M29DW323DT

#### Table 6 – Comparison of different Flash memory commands

Flash Memory works with commands that are passed on the address bus, and it can be seen that the commands vary from different manufacturers. However, as the project uses a PicoBlaze microcontroller it was quite easy to change the software that it runs to use different commands. Luckily, the assembler source code for the PicoBlaze was provided and was commented and structured cleanly. The commands with 'AAA' are changed to '555' and the commands with '555' are changed to 'AAA'. The assembler source was then assembled with the PicoBlaze assembler which generates a VHDL ROM file.

After these changes were made the individual bytes of the Flash memory could be programmed and read back. However, the Atari ST operating system was 192K bytes, so there needs to be a method of programming an entire file to the Flash memory.

## 5.4

## Writing file to Flash Memory

The programmer menu does accept entire files, but of the MCS type. MCS was a file format by Xilinx for storing the FPGA configuration inside a PROM. It's formatted as an ASCII file with each line following the format below.

: [ Address ] [ Data ] [ CR ] [ LF ]

## Figure 22 – MCS file format

The PicoBlaze project expects this file format, so the project was changed with a new choice in the menu to read raw bytes from the serial port and program the Flash memory, incrementing the address on each byte. A test was then done after each byte programmed to see if the address had reached 196608. This way a raw binary file can be transferred and programmed. Appendix C shows the assembler source code for this part of the program.

It's important to use a terminal program that is capable of sending raw binary data. It was found Microsoft's HyperTerminal interprets some of the raw data as terminal control codes and these won't get sent out over the serial port. A rather good freeware program called Realterm which has a vast array of options was used instead of HyperTerminal.

After these changes were made the Flash memory was successfully programmed with the Atari ST operating system, version 1.00.

## CPU

Now it was time for the CPU to be connected to the FPGA. A daughter board was created to be used on the RaggedStones right hand I/O bank. The MC68EC000 and MC68SEC000 feature a  $\overline{\text{MODE}}$  pin which selects the data bus, and as the Atari ST uses a 16 bit data bus this was tied to VCC. Any bidirectional signals, like the CPU data bus are terminated with Xilinx internal pull-ups that were added as constraints into the design.

## 5.6

## Reset

Next was to provide the new CPU with a clock and reset. The Atari ST uses an NE555 timer chip to produce the reset signal. This is activated on power up and whenever the reset button is pressed. A VHDL component was created with a couple of counters, one for a power up reset signal and the other to produce a reset signal when the reset button is pressed.

It is important to have these two different reset signals, as some parts of the design only need to be reset on power up to known states. One of these components was the clock signal component. It was important for the CPU that the clock was running while a reset is issued, and that the reset was active for at least 132 clock cycles [27].

Appendix D lists the VHDL reset component with the RaggedStone switch S1 used as the reset button.

## 5.7

## Clock

The clock component was necessary for generation of clock signals from the master clock, which in the Atari ST was 32 MHz. Below, was the clock frequencies that each component of the Atari ST needs.

- CPU 8 MHz

- GLUE 8 MHz

#### 5.5

- MMU 16 MHz

- SHIFTER 32MHz

- MFP 4 MHz and 2.4576 MHz

- YM2149 2 MHz

- ACIA E Clock and 0.5 MHz

- FDC 8 MHz

- DMA 8 MHz

It was found that it's very important to use the dedicated DCM (Digital Clock Management) PLLs (Phase Locked Loops) that are provided inside the Xilinx Spartan. Using these reduces clock skew and jitter, and also use dedicated global clock routes inside the FPGA. This was to help prevent the clock edges arriving at different times to various components in the FPGA. The DCM can divide a clock from the master frequency and/or multiply it. Without using DCMs the Xilinx ISE software was producing warnings about non dedicated clock routing, and building the project with only small changes was resulting in very significant changes in system stability. As a result of using DCM and dedicated clock routing there was a twofold increase in maximum clock frequency [28], [29], [30].

The MFP in the Atari ST used a dedicated crystal to achieve the 2.4576 MHz frequency. This was used by the MFP for the serial port baud rate. In the FPGA it was possible to use a DCM to create this frequency. The most accurate was to synthesize a 27 MHz clock from the 32 MHz master clock and then divide by 11 to get 2.4545 MHz.

## 5.8

#### Synchronous Bus interface

The ACIA uses the E Clock, which unfortunately the MC68SEC000 CPU doesn't provide. The E Clock was at one tenth of the CPU frequency with a 60/40 duty cycle. The 68SEC000 also doesn't have connections for the VPA or VMA signals.

The E Clock was created by a counter that counts from 0 to 9 and then rolls over. If the value of the counter was 0 to 5 then the E clock was 0, otherwise it will be 1. The Glue component of the Atari ST then asserts the  $\overline{VPA}$ signal to tell the CPU an access to a 6800 synchronous device has been made, which

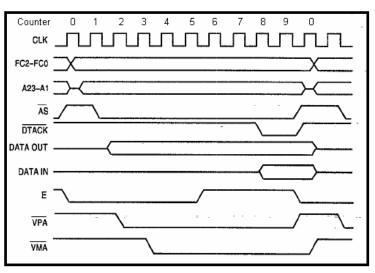

Figure 23 – Synchronous bus interface

in the Atari ST was an access to the Keyboard or Midi ACIA MC6850. The VPA signal was checked when the E Clock counter was 2, and if it was active then  $\overline{VMA}$  was asserted.  $\overline{DTACK}$  was then asserted later when the E Clock counter was 8 or 9 to end the bus cycle. By asserting  $\overline{DTACK}$  late, the CPU automatically inserts wait states. Appendix E shows the Clock VHDL component.

#### 5.9

#### Flash data bus resizing

Now that the clock and reset was provided to the CPU, next was to make the connection

between CPU and Flash memory where the operating system was located. As previously mentioned, the Atari ST had 16 bit wide ROM, but the Raggedstone Flash memory was only 8 bit wide.

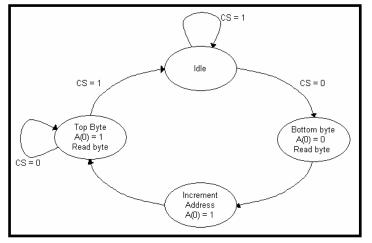

Figure 24 – Flash State machine

As the MC68000 completes a bus cycle in 4 cycles (500ns at 8 MHz), and the Atmel AT49BV040A has an access time of 70ns it's quite possible to fit two 8 bit accesses to the Flash to make it appear 16 bit wide to the CPU. To achieve this, a wrapper VHDL component was created with a FSM (Finite State Machine) controlling latching of data and the LSB of the address. Appendix F shows the VHDL component.

#### 5.10

#### 7 Segment Display

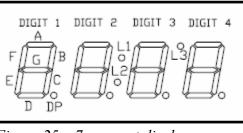

As part of debugging, a VHDL component was created to use the RaggedStone onboard 7 segment display. The RaggedStone has four of these 7 segment displays, enabling 4 hex characters (or 16 bits) to be displayed. This was perfect for displaying the 16 bit data bus, but not the 24 bit address bus. To overcome this limitation, the display will sequence through the upper portion of the address bus, then the lower portion of the address bus and lastly the data bus.

The VHDL component will also be responsible for changing the 4 bit hex value into a value to drive the 7 segment display. The 7 segment displays on the RaggedStone, are just a set of LEDs with no intelligence. Another part it will cater for was scanning the digits of the 7

Figure 25 – 7 segment display

segment display. Only one digit can be displayed at one time, and thus it needs to scan through the digits quick enough for the human eye not to see any flicker. Appendix G shows this VHDL component. One problem encountered was that the mapping for the digits to FPGA pins listed in the RaggedStone user manual appears to be wrong. The table below shows the correct pin mapping.

| Digit 1  | Digit 2   | Digit 3  | Digit 5  |  |

|----------|-----------|----------|----------|--|

| FPGA U14 | FPGA AA17 | FPGA U17 | FPGA U16 |  |

Table 7 – FPGA connections for 7 segment display

## Single Step